Advancements in technology have led to the development of various applications such as self-driving vehicles, target tracking systems, and remote sensors, all of which rely on the high-speed and error-free operation of wireless data transceivers and radar systems. One crucial component in these systems is the phase locked loop (PLL), which assists in the synthesis, modulation, and synchronization of oscillating signals. However, fractional-N PLLs often face challenges such as jitter and fractional spurs, which can degrade the overall performance of these systems.

Challenges in Fractional-N PLLs

Jitter, which refers to the deviation from the ideal timing of the synthesized oscillation, and fractional spurs, which are unwanted signals arising from the periodicity in the error, are common issues in fractional-N PLLs. These challenges can lead to phase noise in the output of the PLL, affecting the overall performance of the system. Digital-to-time converters (DTCs) are typically used in digital PLLs to cancel quantization error, but imperfections in DTCs, known as integral non-linearities (INLs), can result in fractional spurs.

The Proposed Innovative Design Techniques

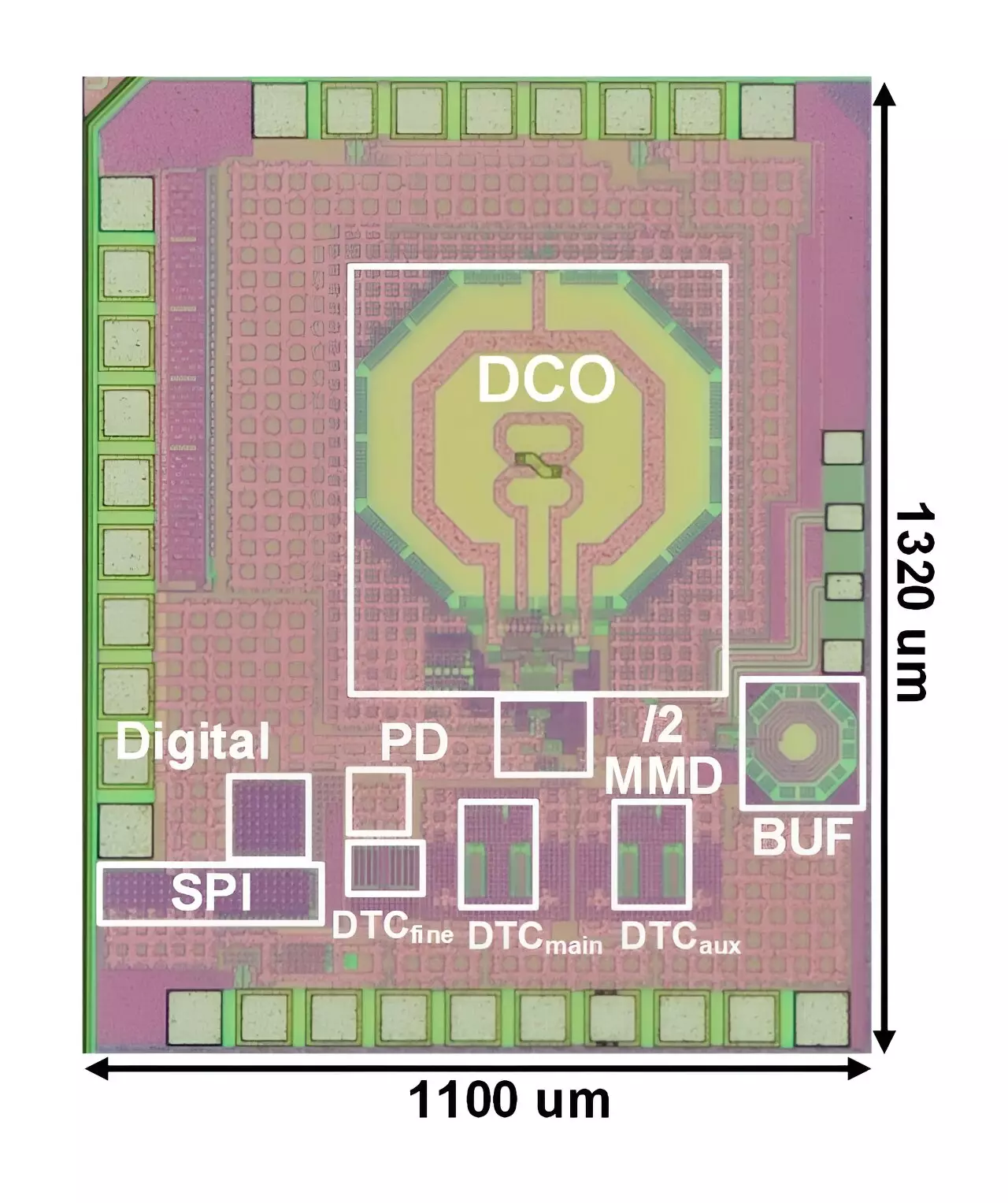

A research team from Tokyo Institute of Technology has developed two innovative design techniques to address these challenges and achieve a low-spur fractional-N PLL. The first technique involves the use of a cascaded-fractional divider, which splits the frequency control word (FCW) into two values that are far from an integer. This approach helps in filtering out high-frequency components, without the need for digital pre-distortion, leading to improved performance in the PLL.

The cascaded-fractional divider technique proposed by the researchers allows for the suppression of fractional spurs by implementing far-from-integer FCWs. This results in a reduction in integrated PLL jitter from 243.5 fs to 143.7 fs, showcasing the effectiveness of this approach in minimizing unwanted signals in the PLL. By avoiding the complexities of digital pre-distortion (DPD), the researchers were able to achieve significant improvements in performance.

The second proposed technique revolves around the use of a pseudo-differential DTC to overcome the limitations of standard DTC implementations. By utilizing two half-range DTCs with even-symmetric INLs in a differential operation, the researchers were able to cancel out the non-linearities of the DTCs. This approach enhanced the performance of the PLL by reducing the fractional-spur level, further improving the overall output quality.

The innovative design techniques developed by the research team from Tokyo Institute of Technology hold promising potential for improving the performance of fractional-N PLLs in various applications. By addressing the challenges of jitter and fractional spurs through the cascaded-fractional divider and pseudo-differential DTC techniques, the researchers have demonstrated significant advancements in PLL technology. These improvements could lead to technological enhancements in wireless communication, autonomous vehicles, surveillance, and tracking systems in the beyond 5G era.

Leave a Reply